# EE 505

Lecture 22

**ADC** Design

Pipeline

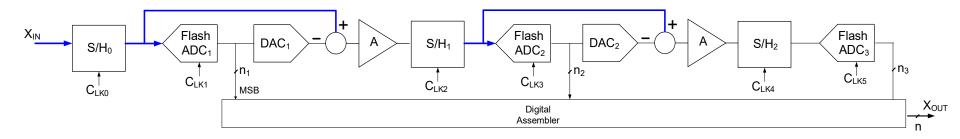

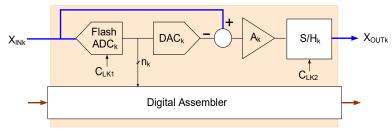

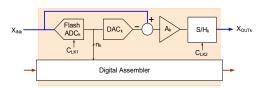

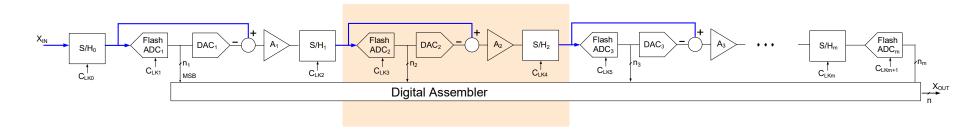

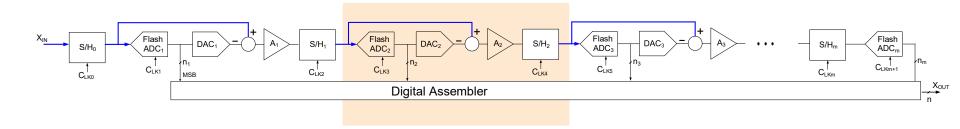

## Three-Step Flash ADC with Interstage Gain and S/H

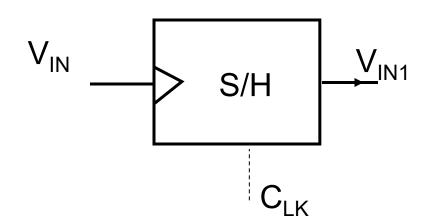

- S/H frees first stage to take another sample during second stage conversion

- This has a pipelining capability

- The pipelined approach dramatically improves speed (close to Flash)

- Significantly reduces the number of comparators

- Introduces latency but not of concern in most applications

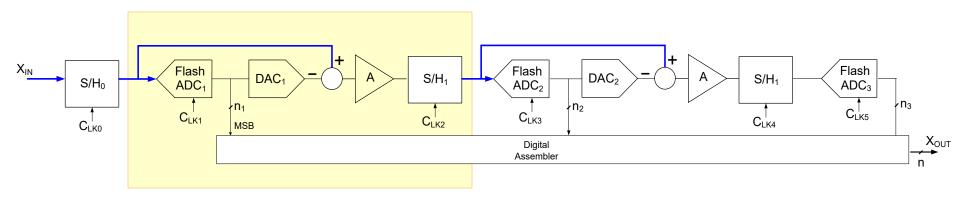

## Three-Step Flash ADC with Interstage Gain

## Can be extended to more than 3 stages

- Can go up to 16 bits or maybe a little higher

- Could be as few as one comparator in each Flash ADC

- Further reduction in number of comparators

(e.g. if one comparator per stage, need only n comparators)

- More latency with more stages but still seldom of concern

- If gains are large enough, comparator offsets in later states can be large

- Will show that with minor modifications, comparator offsets can even be large in first stage

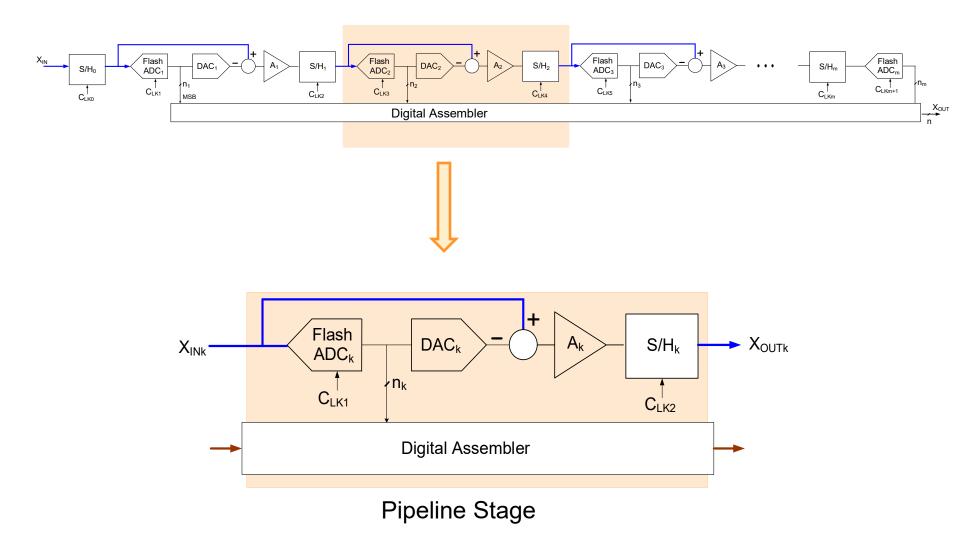

# Pipelined ADC

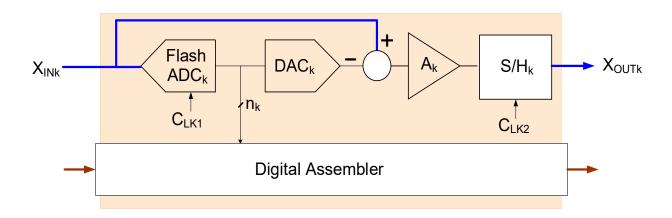

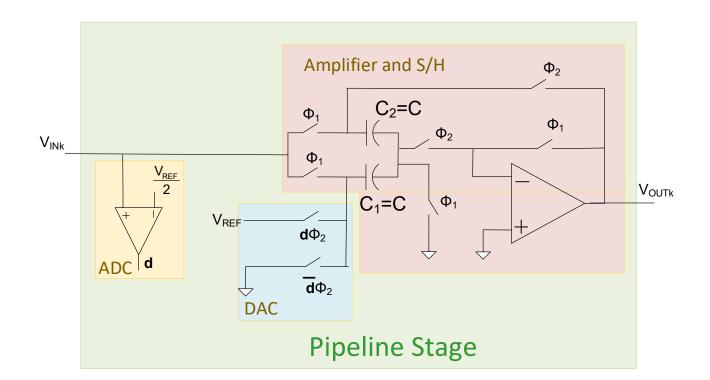

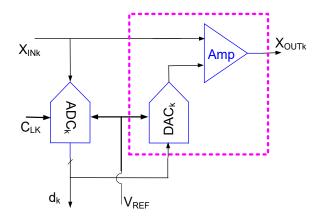

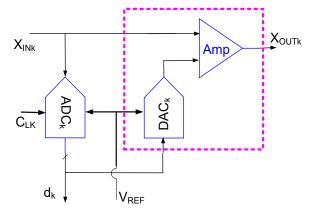

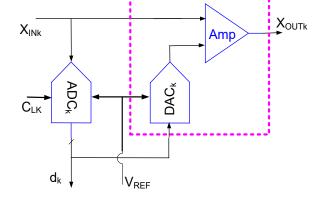

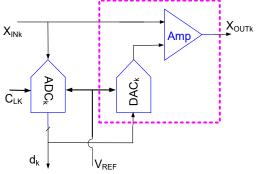

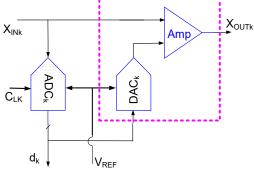

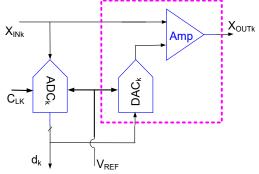

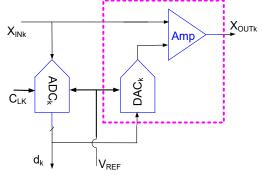

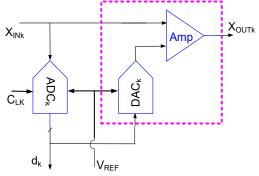

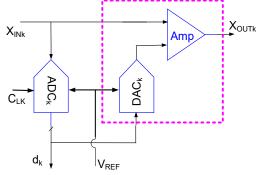

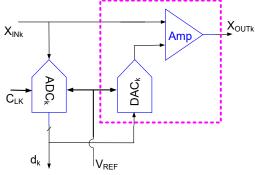

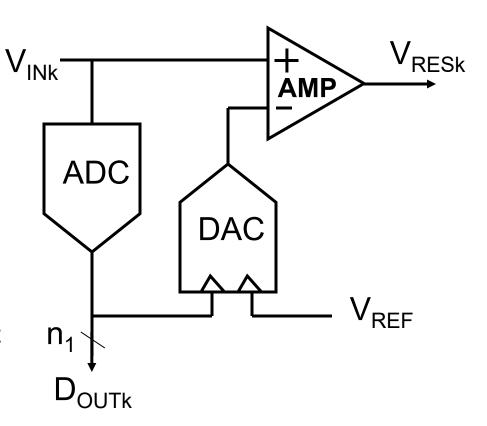

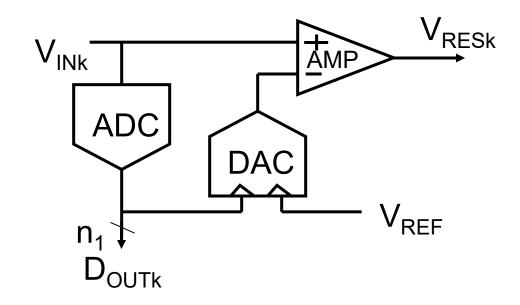

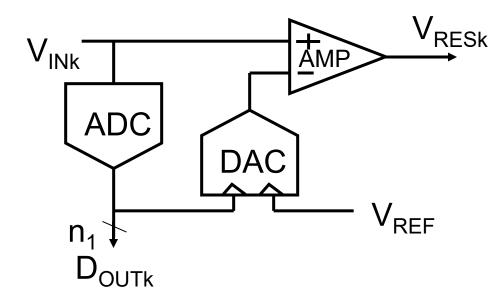

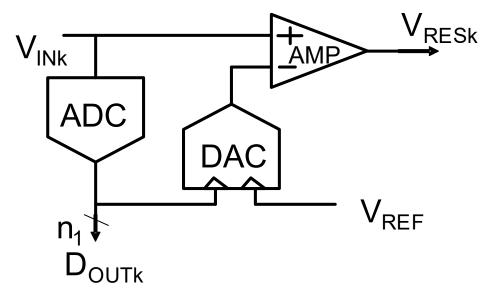

## Pipeline Stage

- Appears to be lots of complexity

- S/H is sampling a near-static signal on all stages (except stage 0)

- Ideally the stage gain is chosen so that the maximum signal level at the output is V<sub>REF</sub> for each stage

- Dominant source of power dissipation is typically the amplifier

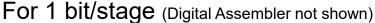

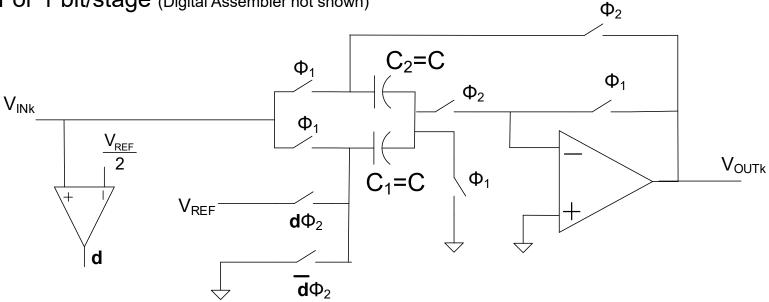

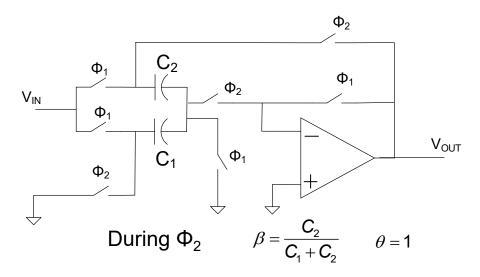

## Typical SC Pipeline Stage

#### Very simple and compact stages are used

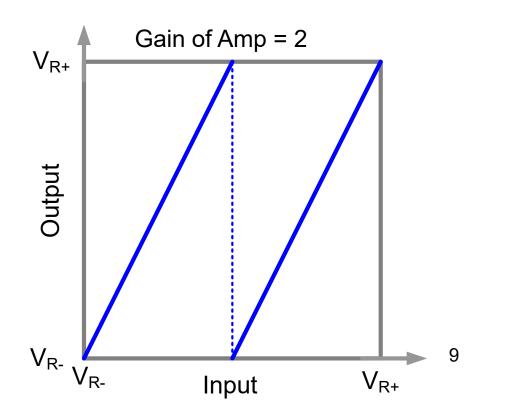

Gain =2

$$V_{\text{out}} = V_{\text{IN}} \left( 1 + \frac{C_{1}}{C_{2}} \right) - d \left( \frac{C_{1}}{C_{2}} \right) V_{\text{REF}}$$

## Typical SC Pipeline Stage

For 1 bit/stage (Digital Assembler not shown)

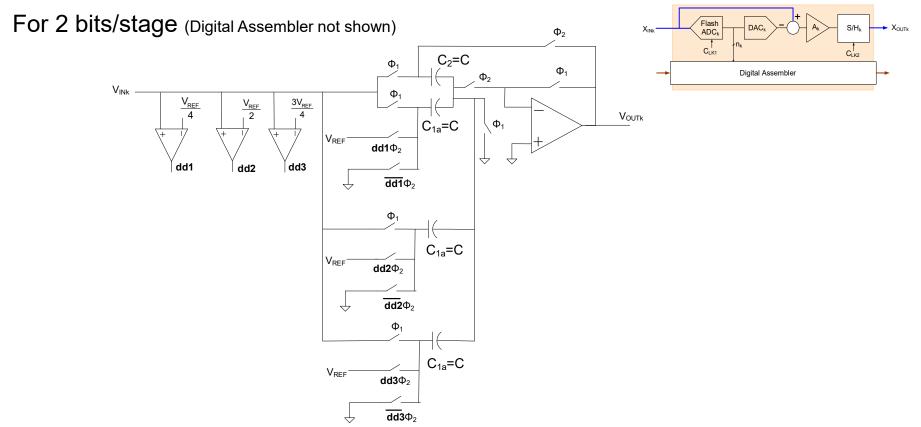

## Typical SC Pipeline Stage

$$V_{\text{out}} = V_{\text{IN}} \left( 1 + \frac{C_{_{1a}} + C_{_{1b}} + C_{_{1c}}}{C_{_{2}}} \right) - \left( d_{_{d1}} \left( \frac{C_{_{1a}}}{C_{_{2}}} \right) + d_{_{d2}} \left( \frac{C_{_{1b}}}{C_{_{2}}} \right) \right) V_{\text{REF}}$$

- Use thermometer code outputs

- Can be extended to more bits/stage

- Accurate gain possible with good layout

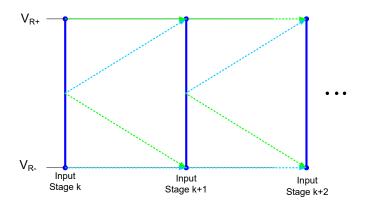

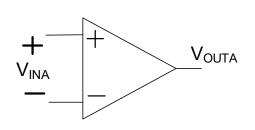

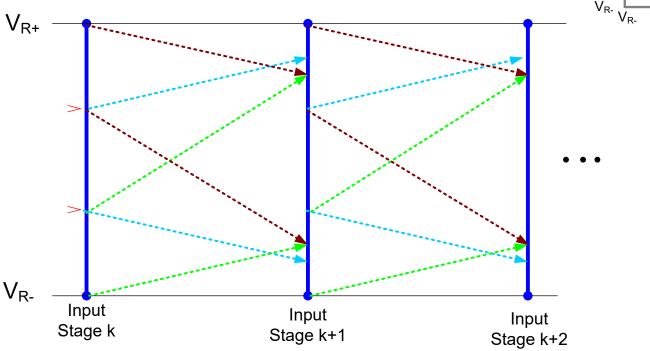

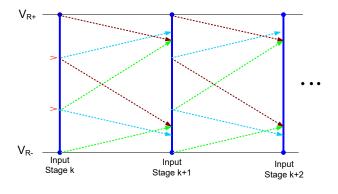

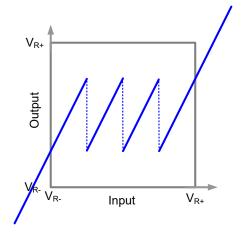

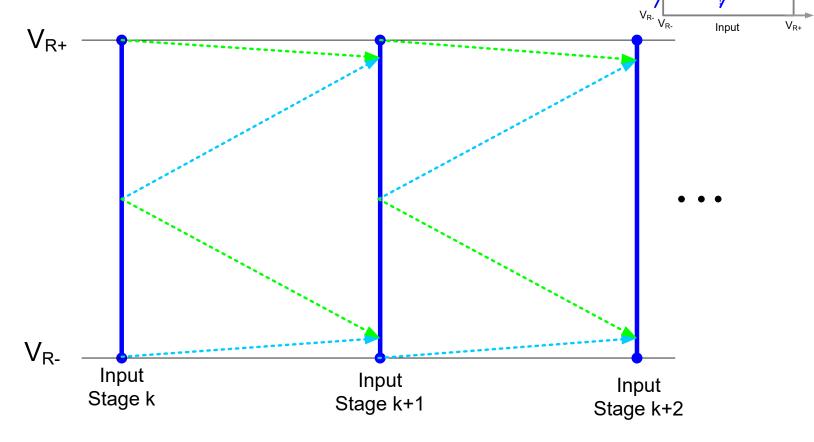

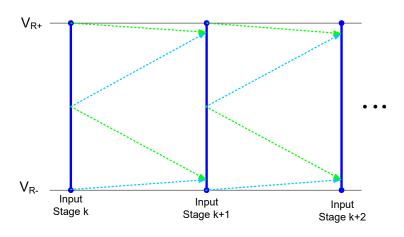

# Operation of Pipelined Amplifier

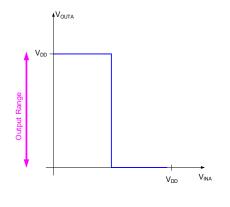

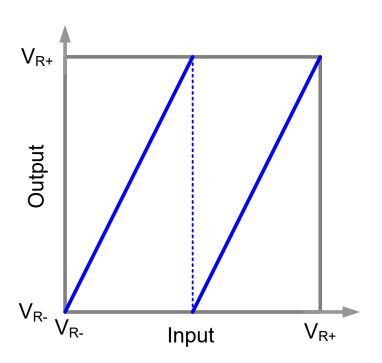

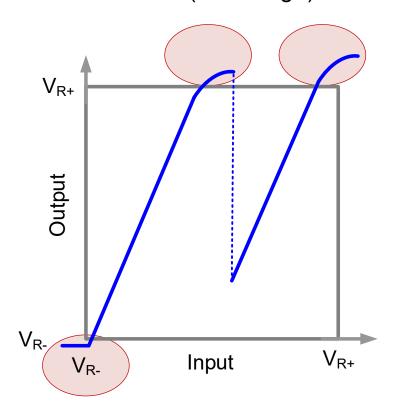

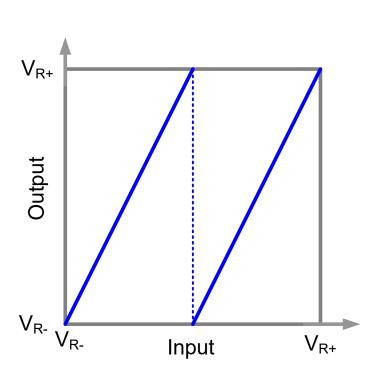

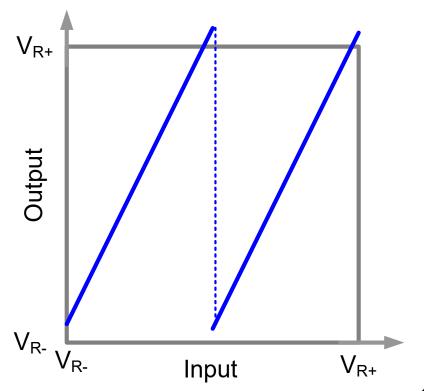

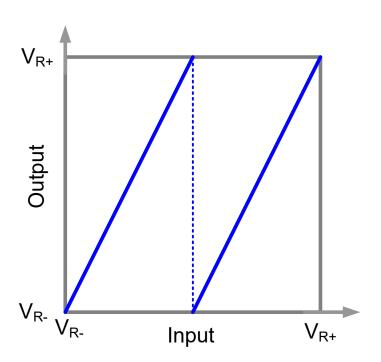

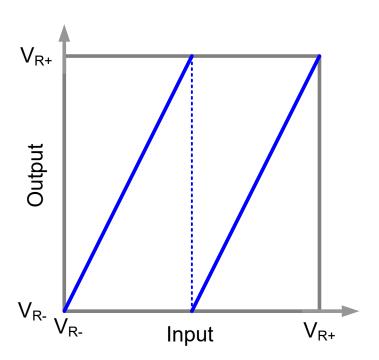

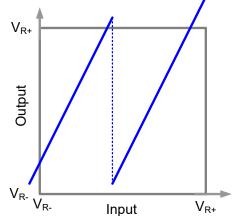

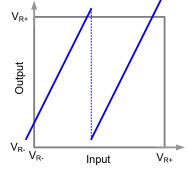

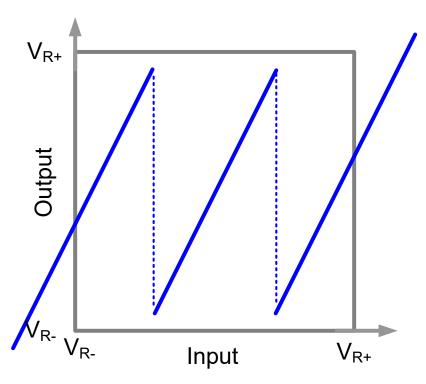

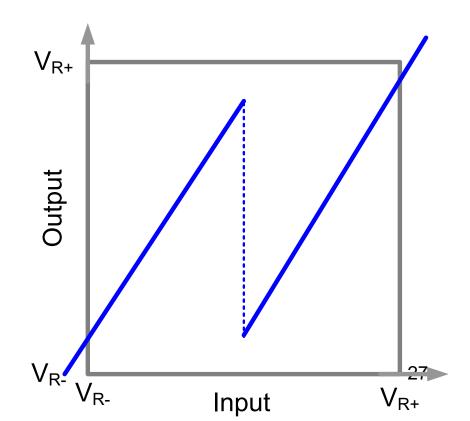

Ideal transfer characteristics (1 bit/stage)

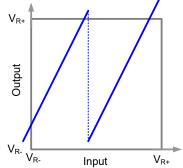

# Interstage Amplifiers

Ideal transfer characteristics (1 bit/stage)

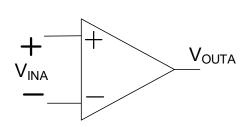

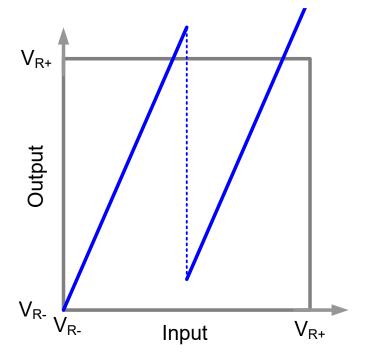

### But what really happens?

$$A_{FB} = \frac{\theta A}{1 + A\beta} \neq \frac{\theta}{\beta}$$

If ideally  $C_1=C_2$  so that ideal gain is 2, will the actual gain be larger or smaller than 2?

#### Depends:

Finite gain of Op Amp tends to make actual gain < 2

Capacitor mismatch could make gain larger or smaller than 2

For reasonable gain in Op Amp, mismatch effects likely will dominate

Ideal transfer characteristics (1 bit/stage)

## But what really happens?

$X_{INk}$

$\overline{C_{LK}}$

ADC<sub>k</sub>

$d_{k} \\$

$X_{OUTk}$

**Amp**

DACk

$V_{REF}$

Ideal transfer characteristics (1 bit/stage)

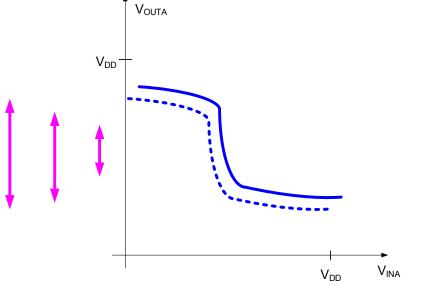

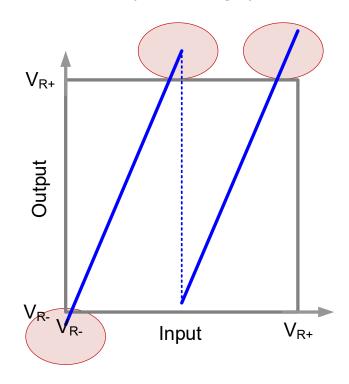

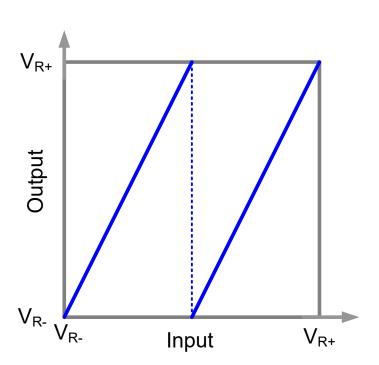

## But what really happens?

Offsets occur as well

Ideal transfer characteristics (1 bit/stage)

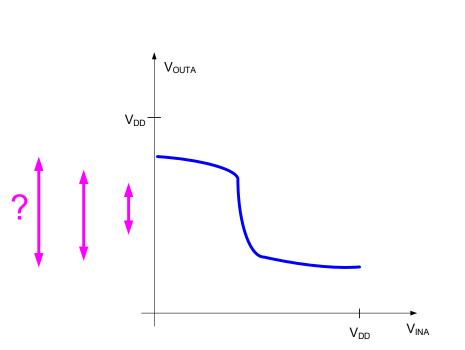

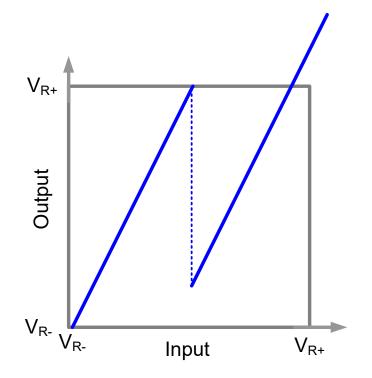

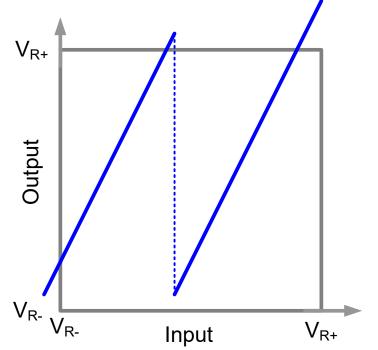

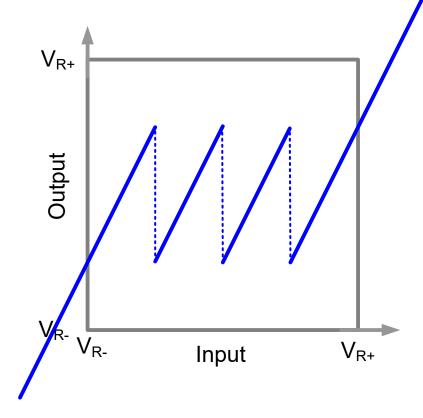

Effect of Gain Error (for A<sub>FB</sub>>2)

Ideal transfer characteristics (1 bit/stage)

Amplifier/DAC/SH block generally designed to operate well only if residue is internal to the I/O Box

Any place where the output extends beyond the I/O box, data converter is vulnerable to loosing data

Ideal transfer characteristics (1 bit/stage)

Possible effects of over-range on transfer characteristics of Amplifier/DAC/SH block

Ideal transfer characteristics (1 bit/stage)

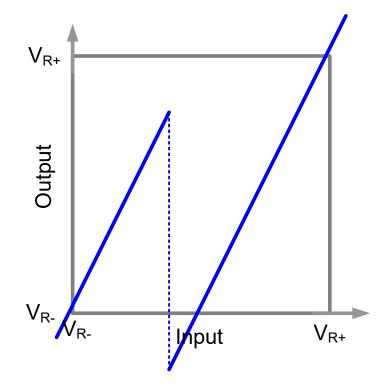

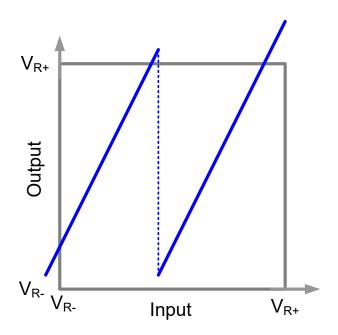

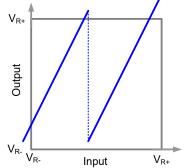

Effect of Amplifier Offset

Ideal transfer characteristics (1 bit/stage)

17

Ideal transfer characteristics (1 bit/stage)

Effect of DAC Errors

Ideal transfer characteristics (1 bit/stage)

Effects of Simultaneous Errors

Ideal transfer characteristics (1 bit/stage)

- Incorrect Interpretation of Digital Output Codes

- Over-range of amplifier Inputs (saturating nonlinearities)

- Over-range of Residue at n-1 stage

Ideal transfer characteristics (1 bit/stage)

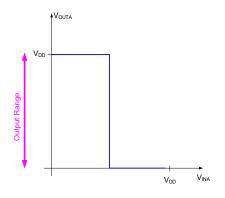

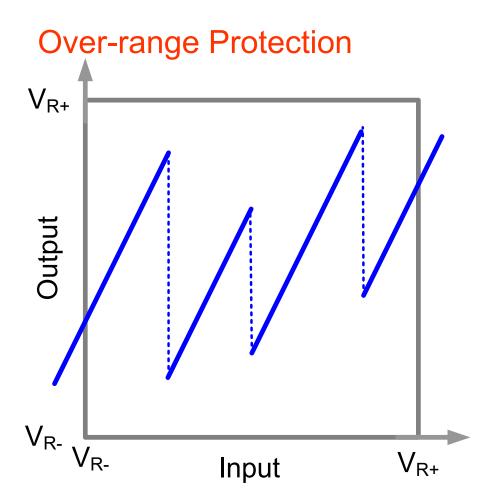

## Over-range Protection

Ideal transfer characteristics (1 bit/stage)

### **Over-range Protection**

Ideal transfer characteristics (1 bit/stage)

Ideal transfer characteristics (1 bit/stage)

Extra comparator levels in ADC (2 extra comparators)

### Issues with out-range protection with extra comparators

Robust to large levels of comparator offset voltage

Increased dynamic power dissipation and loading of V<sub>IN</sub> bus

Increase in area

Ideal transfer characteristics (1 bit/stage)

## Over-range Protection

Sub-radix Structure

Ideal transfer characteristics (1 bit/stage)

## **Over-range Protection**

Sub-radix Structure

### Issues with sub-radix protection

- Robust to large levels of comparator offset voltage

- Requires more involved adders when output code is re-assembled

- Requires additional stages in pipeline (but at LSB end so power and matching requirements are relaxed

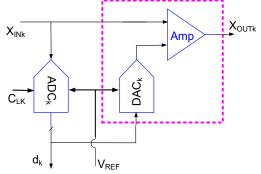

## Pipelined ADC

Claim: If the Amplifiers are linear, settling is complete, comparators have no previous-code dependence and over-range protection is provided, the pipelined ADC makes no errors if the output of the DACs are correctly interpreted

Implication: Flash ADC errors, offsets in comparators and amplifiers, and gain errors in amplifier and S/H do not degrade performance of a pipelined ADC structure!!

# Modeling of a Pipelined ADC

## **Assumptions:**

- All nonlinearities can be neglected

- No previous-code dependence in comparators

- Settling of Amplifiers and DACs is complete

- Over-range protection is provided

# Pseudo-Static Time-Invariant Modeling of a Linear Pipelined ADC

#### Parameterization of Stage k

- Amplifier

- Closed-Loop Gain

- •From input m<sub>1k</sub>

- •From DAC m<sub>2k</sub>

- •From offset m<sub>3k</sub>

- •Offset Voltage V<sub>OSk</sub>

- •DAC

- •V<sub>DACki</sub>

- •ADC

- Offset Voltages V<sub>OSAki</sub>

- Out-Range Circuit (if used and not included in ADC/DAC)

- •DAC Levels V<sub>DACBki</sub>

- •Amplifier Gain m<sub>4k</sub>

# Pseudo-Static Time-Invariant Modeling of a Linear Pipelined ADC

Parameterization of Input S/H Stage

$$V_{in1} = m_{10}V_{in} + m_{20}V_{OS0}$$

# Pseudo-Static Time-Invariant Modeling of a Linear Pipelined ADC

For notational convenience, assume 1 bit/stage

$$V_{RESk} = m_{1k}V_{ink} - d_kV_{DACk}m_{2k} + m_{3k}V_{OSk}$$

## Mathematical Representation of the n Pipelined Stages

$$V_{\text{RES1}} = m_{11} V_{\text{in1}} - d_1 V_{\text{DAC1}} m_{21} + m_{31} V_{\text{OS1}}$$

$$V_{\text{RES2}} = m_{12} V_{\text{in2}} - d_2 V_{\text{DAC2}} m_{22} + m_{32} V_{\text{OS2}}$$

• • •

$$V_{\text{RESk}} = m_{1k} V_{\text{ink}} - d_k V_{\text{DACk}} m_{2k} + m_{3k} V_{\text{OSk}}$$

• • •

$$V_{\text{RES}(\text{n-1})} = m_{\text{1(n-1)}} V_{\text{in(n-1)}} - d_{\text{(n-1)}} V_{\text{DAC(n-1)}} m_{\text{2(n-1)}} + m_{\text{3(n-1)}} V_{\text{OS(n-1)}}$$

Assume for convenience there is also a residue at the last stage

$$V_{\text{RESn}} = m_{1n} V_{\text{inn}} - d_n V_{\text{DACn}} m_{2n} + m_{3n} V_{\text{OSn}}$$

# Mathematical Representation of the Pipelined ADC

$$\begin{split} V_{in1} &= m_{10} V_{in} + m_{20} V_{OS0} \\ V_{RES1} &= m_{11} V_{in1} - d_1 V_{DAC1} m_{21} + m_{31} V_{OS1} \\ V_{RES2} &= m_{12} V_{in2} - d_2 V_{DAC2} m_{22} + m_{32} V_{OS2} \\ & \cdot \cdot \cdot \\ V_{RESk} &= m_{1k} V_{ink} - d_k V_{DACk} m_{2k} + m_{3k} V_{OSk} \\ & \cdot \cdot \cdot \\ V_{RES(n-1)} &= m_{1(n-1)} V_{in(n-1)} - d_{(n-1)} V_{DAC(n-1)} m_{2(n-1)} + m_{3(n-1)} V_{OS(n-1)} \end{split}$$

$V_{RESn} = m_{1n}V_{inn} - d_{n}V_{DACn}m_{2n} + m_{3n}V_{OSn}$

36

## Mathematical Representation of the Pseudo-Static Pipelined ADC

$$\begin{split} V_{in1} &= m_{10} V_{in} + m_{20} V_{OS0} \\ V_{RES1} &= m_{11} V_{in1} - d_1 V_{DAC1} m_{21} + m_{31} V_{OS1} \\ V_{RES2} &= m_{12} V_{in2} - d_2 V_{DAC2} m_{22} + m_{32} V_{OS2} \\ & \cdot \cdot \cdot \\ V_{RESk} &= m_{1k} V_{ink} - d_k V_{DACk} m_{2k} + m_{3k} V_{OSk} \\ V_{RES(n-1)} &= m_{1(n-1)} V_{in(n-1)} - d_{(n-1)} V_{DAC(n-1)} m_{2(n-1)} + m_{3(n-1)} V_{OS(n-1)} \end{split}$$

$$V_{RES(n-1)} = m_{1n} V_{inn} - d_n V_{DACn} m_{2n} + m_{3n} V_{OSn}$$

$$V_{RESk} = V_{in(k+1)}$$

for  $k = 1 \dots n-1$

2n equations relating 2n-1 intermediate nodal voltages and V<sub>in</sub>

37

2n unknowns:

$$\{V_{in1}, V_{in2}, \dots V_{inn}, V_{RES1}, V_{RES2}, \dots V_{RESn-1}, V_{in}\}$$

Want to solve 2n equations for 2n unknowns to obtain  $V_{in}$

#### Mathematical Representation of the Pseudo-Static Pipelined ADC

Eliminating V<sub>RES</sub> terms

$$\begin{split} V_{in1} &= m_{10} V_{in} + m_{20} V_{OS0} \\ V_{in2} &= m_{11} V_{in1} - d_1 V_{DAC1} m_{21} + m_{31} V_{OS1} \\ V_{in3} &= m_{12} V_{in2} - d_2 V_{DAC2} m_{22} + m_{32} V_{OS2} \\ & \cdot \cdot \cdot \\ V_{in(k+1)} &= m_{1k} V_{ink} - d_k V_{DACk} m_{2k} + m_{3k} V_{OSk} \\ & \cdot \cdot \cdot \\ V_{in_n} &= m_{1(n-1)} V_{in(n-1)} - d_{(n-1)} V_{DAC(n-1)} m_{2(n-1)} + m_{3(n-1)} V_{OS(n-1)} \\ V_{RESn} &= m_{1n} V_{inn} - d_n V_{DACn} m_{2n} + m_{3n} V_{OSn} \end{split}$$

n equations relating n intermediate nodal voltages and Vin

n+1 unknowns:

$$\{V_{in1}, V_{in2}, ..., V_{inn}, V_{in}\}$$

38

Want to solve n equations for n+1 unknowns to obtain  $V_{in}$  Appears to **be** over-constrained!

#### Mathematical Representation of the Pseudo-Static Pipelined ADC

Actually, these equations are nested so a solution may proceed by back substitution (ignoring the over-constrained concern)

$$\begin{split} V_{in1} &= m_{10} V_{in} + m_{20} V_{OS0} \\ V_{in} &= \frac{V_{in1}}{m_{10}} - \frac{m_{20}}{m_{10}} \, V_{OS0} \\ V_{in1} &= \frac{V_{in2}}{m_{11}} + d_1 V_{DAC1} \frac{m_{21}}{m_{11}} - \frac{m_{31}}{m_{11}} \, V_{OS1} \\ V_{in} &= \frac{V_{in2}}{m_{10} m_{11}} + d_1 V_{DAC1} \frac{m_{21}}{m_{10} m_{11}} - \frac{m_{31}}{m_{10} m_{11}} \, V_{OS1} - \frac{m_{20}}{m_{10}} \, V_{OS0} \\ V_{in2} &= \frac{1}{m_{12}} \, V_{in3} + d_2 V_{DAC2} \frac{m_{22}}{m_{12}} - \frac{m_{32}}{m_{12}} \, V_{OS2} \\ V_{in} &= \frac{1}{m_{10} m_{11} m_{12}} \, V_{in3} + d_1 V_{DAC1} \frac{m_{21}}{m_{10} m_{11}} + d_2 V_{DAC2} \frac{m_{22}}{m_{10} m_{11} m_{12}} - \frac{m_{32}}{m_{10} m_{11} m_{12}} \, V_{OS1} - \frac{m_{20}}{m_{10}} \, V_{OS0} \end{split}$$

• • •

(Assuming for convenience that  $m_{10}=1$ ,  $V_{OS0}=0$ )

$$V_{in} = \left\{ d_1 \left[ \left( \frac{m_{21}}{m_{11}} \right) V_{DAC1} \right] + d_2 \left[ \left( \frac{m_{22}}{m_{11} m_{12}} \right) V_{DAC2} \right] + \dots + d_n \left[ \left( \frac{m_{2n}}{m_{11} m_{12} \dots m_{1n}} \right) V_{DACn} \right] \right\}$$

$$+ \left\{ \frac{m_{31}}{m_{11}} V_{OS1} + \frac{m_{32}}{m_{11} m_{12}} V_{OS2} + ... + \left( \frac{m_{3n}}{m_{11} m_{12} ... m_{1n}} \right) V_{OSn} \right\}$$

$$+\left\{\frac{V_{RESn}}{m_{11}m_{12}...m_{1n}}\right\}$$

$$V_{\rm in} = \left\{ \frac{d_1 \left[ \left( \frac{m_{21}}{m_{11}} \right) V_{\rm DAC1} \right] + d_2 \left[ \left( \frac{m_{22}}{m_{11} m_{12}} \right) V_{\rm DAC2} \right] + ... + d_n \left[ \left( \frac{m_{2n}}{m_{11} m_{12} ... m_{1n}} \right) V_{\rm DACn} \right] + \frac{V_{\rm REF}}{2^{n+1}} \right\} \\ + \left\{ \frac{m_{31}}{m_{11}} V_{\rm OS1} + \frac{m_{32}}{m_{11} m_{12}} V_{\rm OS2} + ... + \left( \frac{m_{3n}}{m_{11} m_{12} ... m_{1n}} \right) V_{\rm OSn} \right\}$$

$$+ \left\{ \frac{V_{RESn}}{m_{11}m_{12}...m_{1n}} - \frac{V_{REF}}{2^{n+1}} \right\}$$

Code-independent offset term

Code-dependent but can be bounded by ½ LSB with out-range strategy 41

Note: Will not even include last residue amplifier nor create V<sub>RESn</sub>

Note: ADC errors do not affect linearity performance of pipelined structure but DAC outputs and weights are critical

$$V_{_{in}} = \left[ \sum_{_{k=1}^{n}}^{_{n}} d_{_{k}} V_{_{DACk}} \left( \frac{m_{_{2k}}}{\prod\limits_{_{j=1}^{k}}^{_{k}} m_{_{1j}}} \right) + \frac{V_{_{REF}}}{2^{_{n+1}}} \right] \\ + \sum_{_{k=1}^{n}}^{_{n}} V_{_{OSk}} \frac{m_{_{3k}}}{\prod\limits_{_{j=1}^{k}}^{_{k}} m_{_{1j}}} \\ + \left[ \frac{V_{_{RESn}}}{\prod\limits_{_{k=1}^{n}}^{_{n}} m_{_{1k}}} - \frac{V_{_{REF}}}{2^{_{n+1}}} \right]$$

#### If ADC is ideal (lets just verify):

$$m_{ij} = 2$$

,  $V_{DACk} = V_{REF}/2$ ,  $V_{OSk} = 0$

$$V_{in} = \frac{V_{REF}}{2} \sum_{k=1}^{n} \frac{d_k}{2^{k-1}} + \frac{V_{REF}}{2^{n+1}} + \left(\frac{V_{RESn}}{2^n} - \frac{V_{REF}}{2^{n+1}}\right)$$

Performance is as expected

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(offset) + f(residue)$$

$$\alpha_k = V_{\mathrm{DACk}} \frac{m_{2k}}{\displaystyle\prod_{i=1}^k m_{1j}}$$

- f(offset) is code-independent, ideally zero, and causes only overall offset error in ADC

- f(residue) is code-dependent but can be bounded by 1 lsb (causing at most ½ LSB error) with out-range protection

- No errors causing spectral distortion or INL degradation if  $\alpha_k$  are correctly determined

#### Correct Interpretation of Output Code

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(offset) + f(residue)$$

$$\alpha_k = V_{DACk} \frac{m_{2k}}{\displaystyle\prod_{j=1}^k m_{1j}}$$

Natural interpretation of output

$$\vec{D}_{OUT} \neq \langle d_n, d_{n-1}, \dots, d_1 \rangle$$

#### Options:

- 1. Trim all  $m_{jk}$  so that  $\vec{D}_{OUT} = \langle d_n, d_{n-1}, ...d_1 \rangle$

- 2. Make mapping  $<d_n,d_{n-1},...d_1>$  to  $<d'_n,d'_{n-1},...d'_1>$  so that  $\vec{D}_{OUT}=\left<\vec{d'_n},\vec{d'_{n-1}},...d'_1\right>$  (termed digital calibration)

# Pseudo-Static Time-Invariant Modeling of a Linear Pipelined ADC

If more than 1 bit/stage is used and DAC is binarily-weighted structure

$$V_{\scriptscriptstyle{RESk}} = m_{\scriptscriptstyle{1k}} V_{\scriptscriptstyle{ink}} + m_{\scriptscriptstyle{2k}} \left( \sum\limits_{\scriptscriptstyle{j=1}}^{\scriptscriptstyle{2^{n_k}-1}} d_{\scriptscriptstyle{kj}} V_{\scriptscriptstyle{DACkj}} \right) + m_{\scriptscriptstyle{3k}} V_{\scriptscriptstyle{OSk}}$$

# Pseudo-Static Time-Invariant Modeling of a Linear Pipelined ADC

Or, in the most general case:

If DAC is characterized by  $f_k(V_{REF}, \langle d_{ki} \rangle_{i=1}^{n_k})$

$$V_{_{\text{RESk}}} = m_{_{1k}}V_{_{\text{ink}}} + m_{_{2k}}\left(f_{_{k}}\left(V_{_{\text{REF}}},\left\langle d_{_{kj}}\right\rangle_{_{j=1}}^{_{n_{_{k}}}}\right)\right) + m_{_{3k}}V_{_{OSk}}$$

If more than 1 bit/stage is used and DAC is binarilyweighted structure

$$V_{_{in}} = \left[ \sum\limits_{_{k=1}^{n}}^{_{n}} \left( \sum\limits_{_{j=1}^{n-n_{k_{j}}}}^{_{n-n_{k_{j}}}} d_{_{k_{j}}} V_{_{DACk_{j}}} \right) \left( \frac{m_{_{2k}}}{\prod\limits_{_{j=1}^{n}}^{_{k}} m_{_{1j}}} \right) + \frac{V_{_{REF}}}{2^{_{n+1}}} \right] \\ + \sum\limits_{_{k=1}^{n}}^{_{n}} V_{_{OSk}} \frac{m_{_{3k}}}{\prod\limits_{_{j=1}^{n}}^{_{k}} m_{_{1j}}} \\ + \left[ \frac{V_{_{RESn}}}{\prod\limits_{_{k=1}^{n}}^{_{n}} m_{_{1k}}} - \frac{V_{_{REF}}}{2^{_{n+1}}} \right]$$

If DAC is characterized by  $f_k(V_{REF}, \langle d_{ki} \rangle_{i=1}^{n_k})$

$$f_{_k}\left(V_{_{

m REF}},\left\langle d_{_{

m kj}}

ight

angle_{_{j=1}}^{n_k}$$

$$V_{_{in}} = \Bigg[ \sum\limits_{_{k=1}^{n}}^{_{n}} \Big( f_{_{k}} \Big( V_{_{REF}}, \Big\langle d_{_{kj}} \Big\rangle_{_{j=1}^{n}}^{_{n_{k}}} \Big) \Big) \Bigg( \frac{m_{_{2k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{1j}}} \Bigg) + \frac{V_{_{REF}}}{2^{_{n+1}}} \Bigg] \\ + \sum\limits_{_{k=1}^{n}}^{_{n}} V_{_{OSk}} \frac{m_{_{3k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{1j}}} \\ + \Bigg[ \frac{V_{_{RESn}}}{\prod\limits_{_{k=1}^{n}}^{_{m}} m_{_{1k}}} - \frac{V_{_{REF}}}{2^{_{n+1}}} \Bigg] \\ + \sum\limits_{_{k=1}^{n}}^{_{n}} V_{_{OSk}} \frac{m_{_{3k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{1j}}} \\ + \sum\limits_{_{k=1}^{n}}^{_{n}} m_{_{1k}} - \frac{V_{_{REF}}}{2^{_{n+1}}} \Bigg] \\ + \sum\limits_{_{k=1}^{n}}^{_{n}} V_{_{OSk}} \frac{m_{_{2k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{1j}}} \\ + \sum\limits_{_{k=1}^{n}}^{_{n}} V_{_{OSk}} \frac{m_{_{2k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{1j}}} \\ + \sum\limits_{_{k=1}^{n}}^{_{n}} V_{_{NSk}} \frac{m_{_{2k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{2k}}} \\ + \sum\limits_{_{k=1}^{n}}^{_{k}} V_{_{k}} \frac{m_{_{2k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{2k}}} \\ + \sum\limits_{_{k=1}^{n}}^{_{k}} V_{_{k}} \frac{m_{_{k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{j}}} \\ + \sum\limits_{_{k=1}^{n}}^{_{k}} V_{_{k}} \frac{m_{_{k}}}{\prod\limits_{_{j=1}^{m}}^{_{k}} m_{_{k}}} \\ + \sum\limits_{_{k=1}^{n}}^{_{k}} V_{_{k}} \frac{m_$$

No errors causing spectral distortion or INL degradation if terms involving  $d_{ki}$  are correctly determined

### Pseudo-Static Characterization of Pipelined ADC with Arbitrary Bits/Stage and Out-Range Protection

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(offset) + f(residue)$$

- d<sub>k</sub> are boolean output variables from stage ADCs (including out-range protection if included)

- the  $\alpha_k$  are functions of DAC levels and amplifier gains

- f(offset) is code-independent, ideally zero and causes only overall offset error in ADC

- f(residue) is code-dependent but can be bounded by 1 lsb (causing at most ½ LSB error) with out-range protection

- Equation applies to both sub-radix2 and extra comparator out-range protection

- •No errors causing spectral distortion or INL degradation if  $\alpha_{\mathbf{k}}$  are correctly determined

#### **Observations**

$$\begin{split} V_{in} &= \sum_{k=1}^{n} \alpha_k d_k \ + \ \textit{f(offset)} \ + \textit{f(residue)} \\ \text{form of} \quad \alpha_k \ : \ V_{\mathrm{DACk}} \frac{m_{2k}}{\prod\limits_{i=1}^{k} m_{1j}} \end{split}$$

- Substantial errors are introduced if  $\alpha_k$  are not correctly interpreted!

- Some calibration and design strategies focus on accurately setting gains and DAC levels

- Analog calibration can be accomplished with either DAC level or gain calibration

- Digital calibration based upon coefficient identification does not require accurate gains or precise DAC levels

#### Observations (cont)

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(offset) + f(residue)$$

form of

$$\alpha_k: V_{\mathrm{DACk}} \frac{m_{2k}}{\displaystyle\prod_{j=1}^k m_{1j}}$$

- If nonlinearities are avoided, data conversion process with a pipelined architecture is extremely accurate

- Major challenge at low frequencies is accurately interpreting the digital output codes

#### Pipelined ADC

Claim: If the Amplifiers are linear, settling is complete, comparators have no previous-code dependence, and over-range protection is provided, the pipelined ADC makes no nonlinearity errors if the output of the DACs are correctly interpreted

Implication: Flash ADC errors, offsets in comparators and amplifiers, and gain errors in amplifier and S/H do not degrade linearity performance of a well-designed pipelined ADC structure!!

Approach to pipelined ADC design:

- Design so no nonlinear errors are present

- Recognize that component matching is not critical!

- Correctly interpret output codes (some type of calibration)

#### Observations (cont)

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(offset) + f(residue)$$

form of

$$\alpha_k: V_{DACk} \frac{m_{2k}}{\displaystyle\prod_{j=1}^k m_{1j}}$$

• If nonlinearities are present, this analysis falls apart and the behavior of the ADC is unpredictable!

# Pseudo-Static Characterization of Pipelined ADC with <u>Arbitrary Bits/Stage</u> and Out-Range Protection

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(offset) + f(residue)$$

No errors causing spectral distortion or INL degradation if  $\alpha_k$  are correctly determined and last residue is variability bounded

$\alpha_k$  terms are random variables at the design stage but deterministic at the chip level f(residue) is random at the design stage but deterministic at the chip level

#### **Key Questions:**

How can the correct determination of the  $\alpha_k$  terms be guaranteed?

How can a required bound of f(residue) be achieved?

## Approaches to Correctly Interpreting Output Codes

- 1. Design all components and blocks to be sufficiently ideal to achieve target performance with high yield (natural interpretation of output codes)

- 2. Reduce design requirements on components and blocks and use calibration (analog or digital) to achieve target performance with high yield

- Try to achieve ideal performance and use calibration to overcome deficiencies in design

Which approach does industry dominantly follow today?

Which approach shows the most promise for low voltage, high speed, high resolution design?

Why is approach 3 not the most attractive approach to follow?

Can not derive enough speed and area benefits in emerging processes (Remember assumption of linearity is still being made)

Stay Safe and Stay Healthy!

## End of Lecture 22